Logic Diagram Of 1 Bit Adder 49++ Images Result

Logic Diagram Of 1 Bit Adder. The full adder is usually a component in a cascade of adders, which add 8, 16, 32, etc. The equation or expression of the full adder is are, and they are as follows.

⊕ is the symbol of the xor operation. From the above equation of the sum s, it is easily visible that first a and b are xored together, then cin. In the above table, 'a' and' b' are the input variables.

aeb 1 8t wiring diagram 71 beetle hazard switch wiring diagram wiring actuator cushman truckster 36 volt wiring diagram

CircuitVerse 1 bit full adder

The half adder is used to add only two numbers. Thus, the equations can be written as The full adder, described in the next section, solves. ⊕ is the symbol of the xor operation.

Source: circuitverse.org

⊕ is the symbol of the xor operation. 2 bit comparator 2 bits logic digital circuit. The equation or expression of the full adder is are, and they are as follows. The half adder is used to add only two numbers. A technique for leakage reduction in nanoscale domino.

Source: researchgate.net

From the above equation of the sum s, it is easily visible that first a and b are xored together, then cin. These are the instructions to play with the circuit: 2 bit comparator 2 bits logic digital circuit. A full adder within digital logic. Block diagram of full adder.

Source: researchgate.net

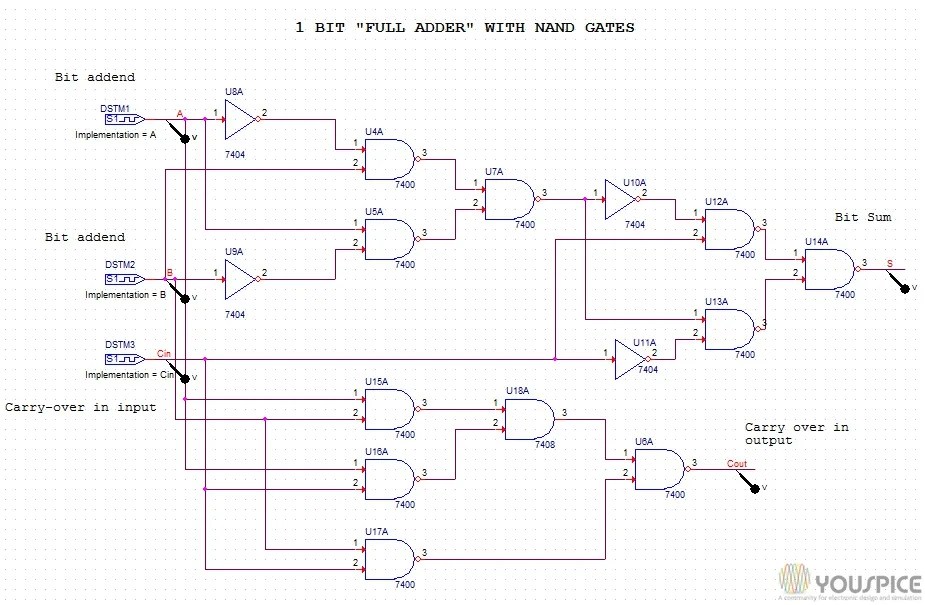

Two input xor gate, two input and gate, two input or gate forms the full adder logic circuit, input & output of this logic diagram can be derived by the following truth table. To run the simulation with these new values, click on the continue value. The full adder is an added that takes three inputs &generates two outputs as.

Source: circuitverse.org

Our aim is to build the full adder circuit using multiplexers rather than the usual basic logic gates. 1 bit full adder : The block diagram of full added is as shown below: The higher significant bit of this result is called a carry. Half adder is implemented by 21/p xor and 2.

Source: youspice.com

Vhdl code for full adder coding computer science binary number. S = a ⊕ b⊕cin. Full adder using two half adders half full electronics circuit. In the above table, 'a' and' b' are the input variables. Two input xor gate, two input and gate, two input or gate forms the full adder logic circuit, input & output of this logic.

Source: schematics.com

An adder is a digital electronic circuit that performs addition of numbers. The equation or expression of the full adder is are, and they are as follows. Full adder logic gate diagram. Adders are used in every single computer's processors to add various numbers, and they are used in. These are the instructions to play with the circuit:

Source: electronics.stackexchange.com

Vhdl code for full adder coding computer science binary number. In the above table, 'a' and' b' are the input variables. However, the half adder lacks a c in input to accept the c out of the previous column. 0+0+0 = 0 0+0+1 = 1 0+1+0 = 1 0+1+1 = 10. Come up with a truth table and logic diagram.

Source: electronics-tutorial.net

For the adder chip, use the logic symbol in the first page. Full adder logic gate diagram. The block diagram of full added is as shown below: 1 bit full adder logic diagram. To overcome this problem, the full adder was developed.

Source: engineeringproblemsandanswers.blogspot.com

0+0+0 = 0 0+0+1 = 1 0+1+0 = 1 0+1+1 = 10. A full adder within digital logic. A technique for leakage reduction in nanoscale domino. The higher significant bit of this result is called a carry. Implementation of full adder using half adders 2 half adders and a or gate is required to implement a full adder.

Source: forum.allaboutcircuits.com

A technique for leakage reduction in nanoscale domino. 1 bit full adder logic diagram 1 full adder block diagram. To run the simulation with these new values, click on the continue value. Vhdl code for full adder coding computer science binary number.

Source: maxcruz-mylife.blogspot.com

From the above equation of the sum s, it is easily visible that first a and b are xored together, then cin. 1 bit full adder logic diagram However, the half adder lacks a c in input to accept the c out of the previous column. 5 32 decoder circuit logic circuit electronics circuit. The half adder is used to.

Source: cs.cornell.edu

Two input xor gate, two input and gate, two input or gate forms the full adder logic circuit, input & output of this logic diagram can be derived by the following truth table. Need help with logic gates and circuits i have no idea how to do this if possible please provide an explanation as to how you arrived at.

Source: researchgate.net

The higher significant bit of this result is called a carry. A technique for leakage reduction in nanoscale domino. Implementation of full adder using half adders 2 half adders and a or gate is required to implement a full adder. To overcome this problem, the full adder was developed. Full adder using two half adders half full electronics circuit.

Source: researchgate.net

The equation or expression of the full adder is are, and they are as follows. Full adder logic gate diagram. A full adder is implemented using 2 half adder and 2 i/p or gate. The full adder is usually a component in a cascade of adders, which add 8, 16, 32, etc. Vhdl code for full adder coding computer science.

Source: chegg.com

The full adder, described in the next section, solves. However, the half adder lacks a c in input to accept the c out of the previous column. 2 bit comparator 2 bits logic digital circuit. 1 bit full adder : Vhdl code for full adder coding computer science binary number.

Source: researchgate.net

Implementation of full adder using half adders 2 half adders and a or gate is required to implement a full adder. A technique for leakage reduction in nanoscale domino. 2 bit comparator 2 bits logic digital circuit. To overcome this problem, the full adder was developed. 5 32 decoder circuit logic circuit electronics circuit.

Source: multisim.com

The equation or expression of the full adder is are, and they are as follows. These are the instructions to play with the circuit: A technique for leakage reduction in nanoscale domino. Full adder logic gate diagram. The result sum is exclusively addition between a,b,cin then result carry is or logic operation between a.b then a⊕b and cin.

Source: researchgate.net

The first three operations produce a sum whose length is one digit, but when both augund and addend bits are equal to 1, the binary sum consists of two digits. Full adder using two half adders half full electronics circuit. Draw the logic diagram of a 1 bit half adder. On the other hand, the full adder circuit performs the.

Source: researchgate.net

The equation or expression of the full adder is are, and they are as follows. Let’s see an addition of single bits. The full adder has three input states and two output states i.e., sum and carry. The higher significant bit of this result is called a carry. Come up with a truth table and logic diagram for the bcd.

Source: diagramblog.blogspot.com

However, the half adder lacks a c in input to accept the c out of the previous column. This simple addition consist of 4 possible operations, they are 0+0=0, 0+1=1, 1+0=1, 1+1=1 and 1+1=10. Full adder logic gate diagram. In the above table, 'a' and' b' are the input variables. Cout = (ab) + (cin (a⊕b)).